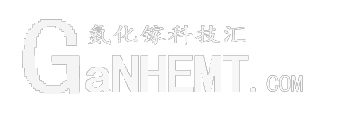

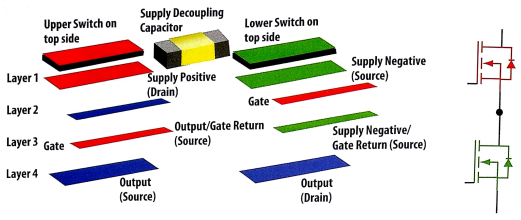

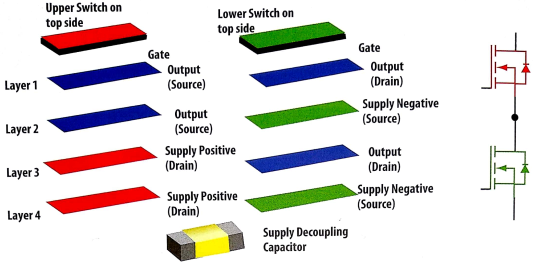

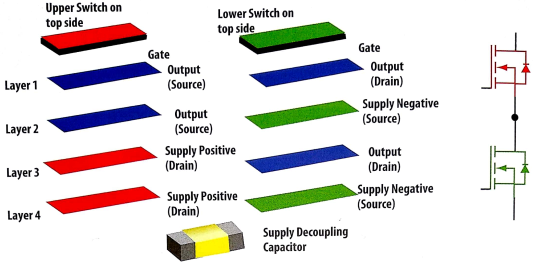

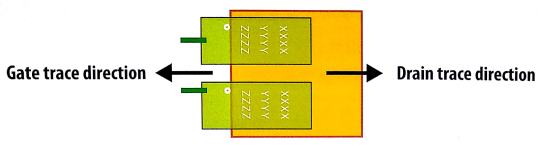

信号层和电源层的分配是设计版图非常重要的一环,是为完成后的设计提供电场和磁场屏蔽的一个有效方法。屏蔽栅极信号免于漏极具高dv/dt至为重要。设计的实现方式也可以影响最好的解决方案。举例来说,焊接单个组件在电路板的一面(如只是焊接一个eGaN FET在板的一面)。最理想的层板分配如图1所示。虽然栅极与漏极层之间有很好的屏蔽,去耦电容器必须放置在电路板的位置是与eGaN FET同一侧。连接至去桐电容器的电容,有可能比图2所显示较实际的解决方案,把去耦电容器放在电路板底部的电容为大。但底部器件的栅极信号,现在是通过电容耦合至漏极。在版图设计上,为了减小栅极信号层和漏极层之间的电容,设计工程师可以像图3那样把它们以相反方向隔开,以增加板之间的间距。

图1 一个四层的印刷电路板的上部含eGaN FET,其最理想的层板分配。

图2 一个四层的印刷电路板的上部含eGaN FET,其实际的层板分配。

图3 在单个层板利用空间的分隔替栅极及漏极解藕。

图2 一个四层的印刷电路板的上部含eGaN FET,其实际的层板分配。

图3 在单个层板利用空间的分隔替栅极及漏极解藕。