PIF的定义由下列公式给出:

(1)

(1)dvn/dt=从实际dvn/dt·Kv推导得出的n个并联器件的电压抗扰度限值[1s/s],其中Kv=1[1/V]

din/dt=从实际din/dt·Ki推导得出的n个并联器件的电流抗扰度限值[1/s],其中Ki=1[1/A]

dv1/dt=从实际 dv/dt·Kv推导得出的单器件形式的转换器的电压抗扰度限值[1/s],其中Kv=1[1/V]

di1/dt=从实际dv/dt·Ki推导得出的单器件形式的转换器的电流抗扰度限值[1/s],其中Ki=1[1/A]

n代表在每个开关并联器件的数目。

PIF可以理解为并联eGaN FET转换器,相对含单个器件转换器的开关功率损耗倍增因子。

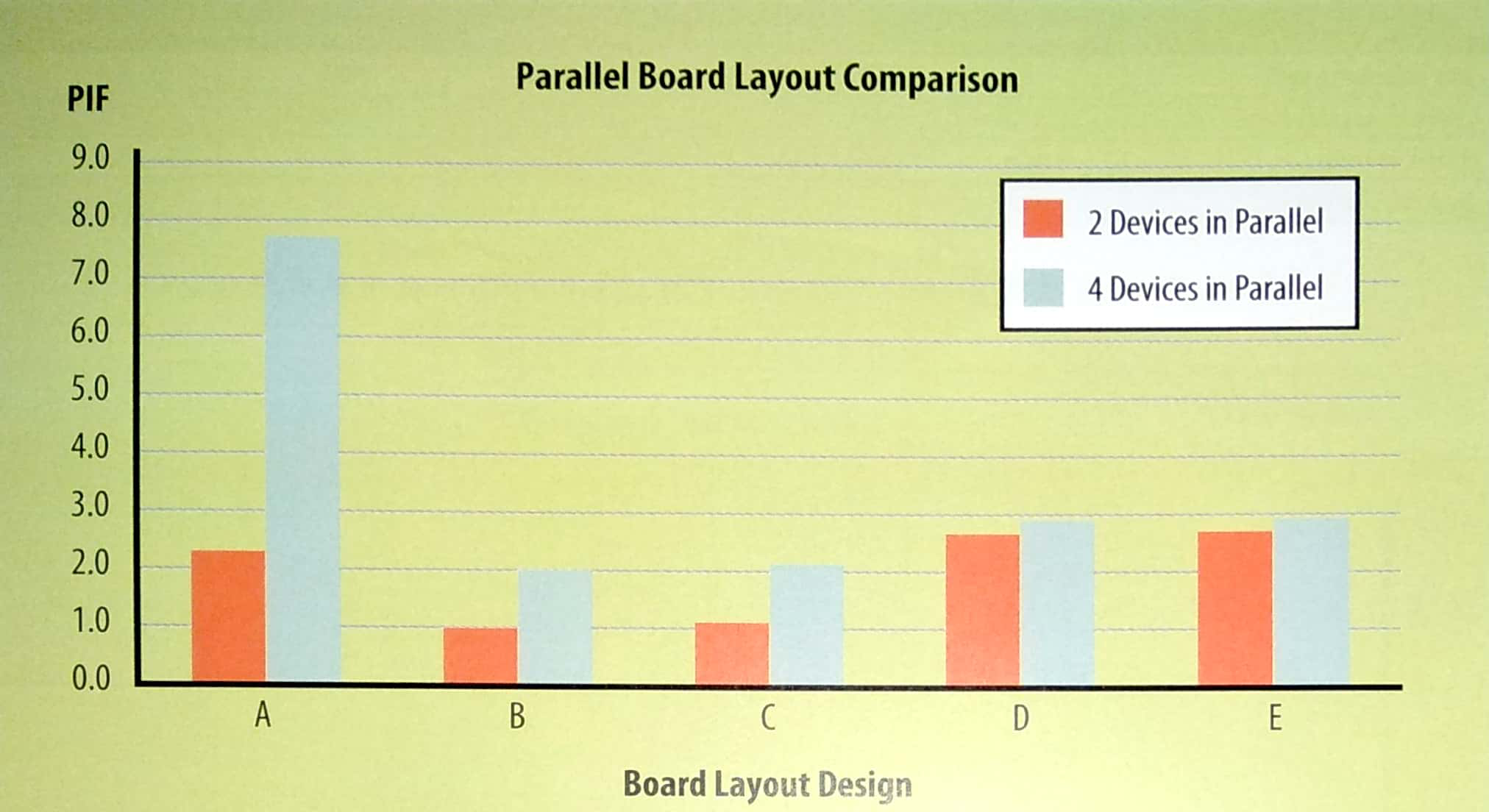

使用公式1并规范化为相比的含单个器件的设计,可以得出每个评估设计使用两个和四个并联eGaN FET的规范化PIF图表(见图1)。

图1 使用两个和四个并联eGaN FET的不同版图的开关PIF比较。单个器件的PIF为1.0。

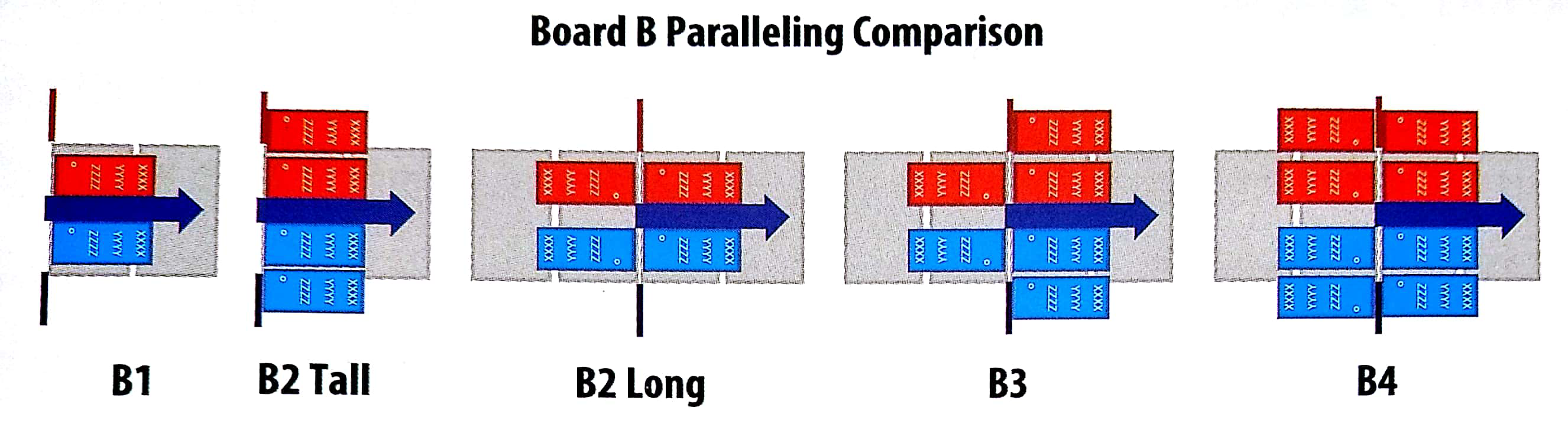

从图1 PIF的结果可以看到,使用两个eGaN FET的B设计明显是最好的设计,而使用四个eGaN FET的A设计是最差的。我们可以更详细地研究B设计,了解并联器件的数量如何影响转换器的性能。图2展示了并联不同数量的eGaN FET的B设计的不同版图。

图2 并联不同数量的eGaN FET的设计B的各种可选版图。

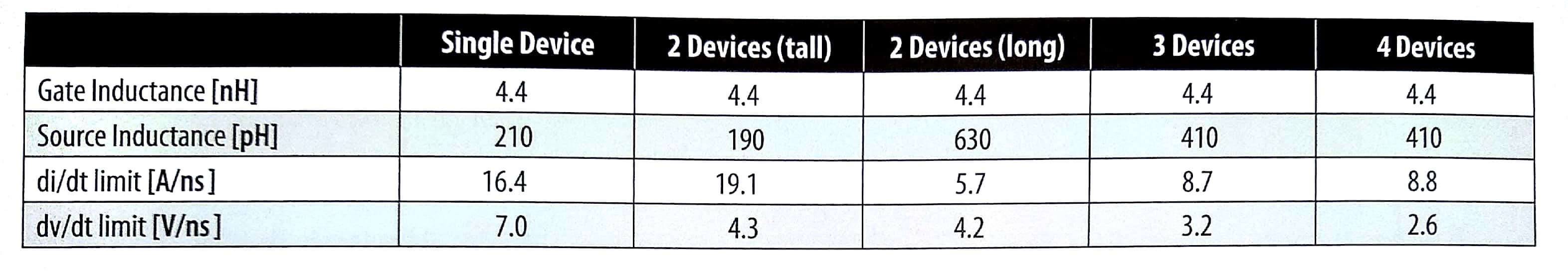

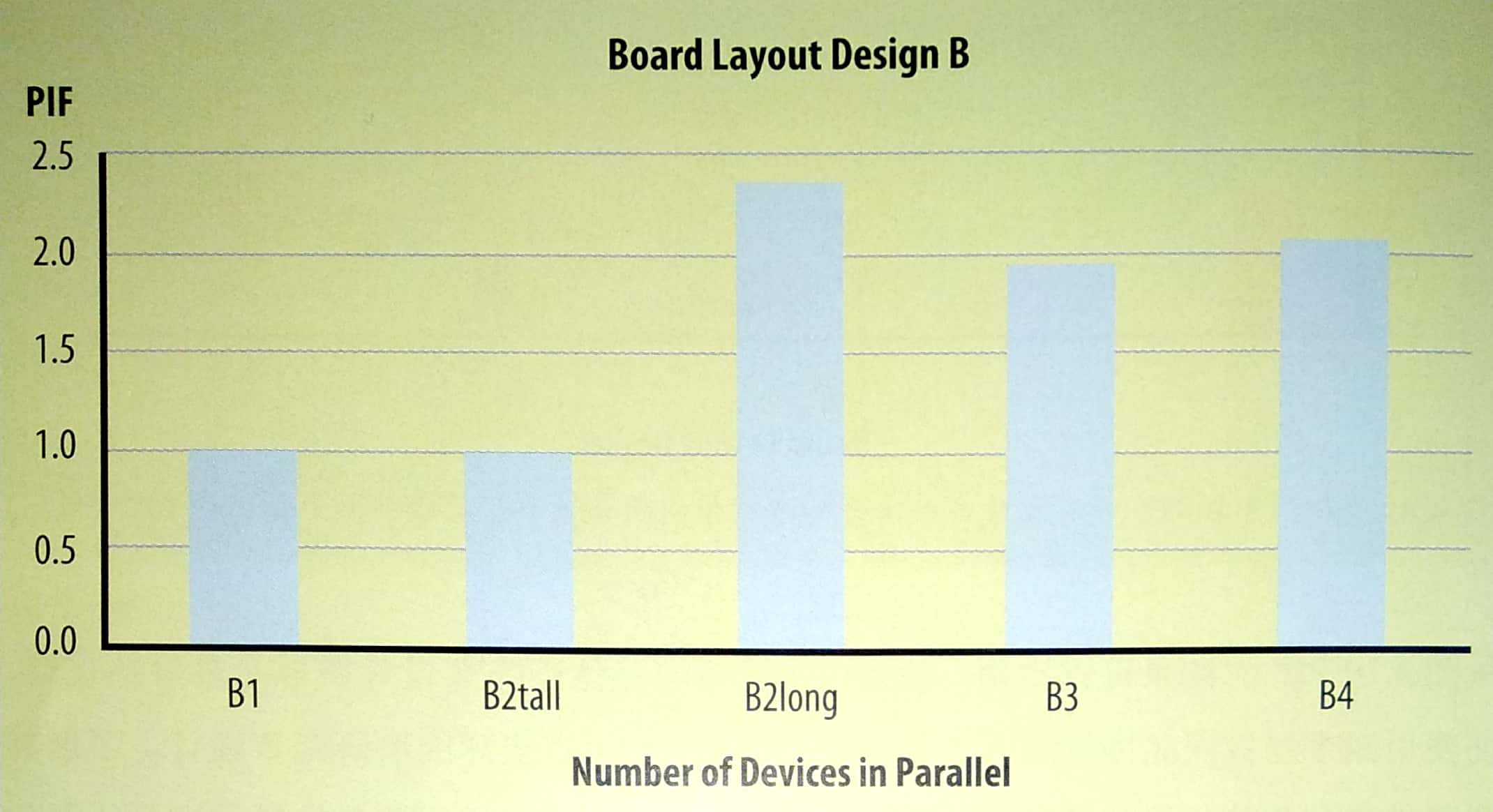

表1给出了图2所示设计的电感值及抗扰极限值。图3给出了并联不同数量eGaN FET所得的B设计,包括使用了两个并联eGaN FET的版图,并规范化为相比的含单个器件设计的PIF图表。

表1 针对图2所示的不同情况下所计算的电感和抗干扰极限值。

图3 并联不同敷量eGaN FET所得的B设计的并联影响因数。