器件之间的共源电感在栅极环路中是共享的,可能会影响电压,导致不期望的开关导通或关断。公式(1)给出了在di/dt事件发生时,由共源电感引入栅极的电压值。将感应电压的极限值设置为栅极阈值电压后,我们就可以确定一个设计的di/dt极限值。

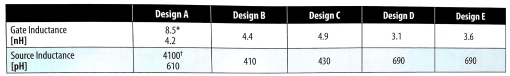

经过对五个设计的分析与测量得出的栅极和源极电感值见表1。

+较大值是每对器件之间的电感,较小值是一对器件之间的电感。

表1 经过评估的五个版图设计,每一个设计的栅极和源极电感。

使用表1中的电感值及典型的阈值电压(VTH),我们可以得出每个被评估的设计在使用四个并联FET时的di/dt极限值,如表2所示。

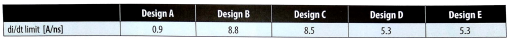

表2 针对五个设计样例得出的di/dt极限值。

从表2的结果可以看出,A设计的di/dt抗扰度比其它设计要差得多。这个设计的目的就是要指出这是一个不正确的并联eGaN FET的方法,而这个方法看起来却似乎很有吸引力,因为这个方法的供电环路具非常小的去耦电感。

评佔使用并联eGaN FET开关的dv/dt抗扰度

漏极至源极上的快速电压过渡过程(当dv/dt事件发生时),可能将电流透过栅极至漏极米勒电容引入栅极电路。当开关关断,同时在半桥拓扑中的对立开关导通时,这种情况就通常会发生。

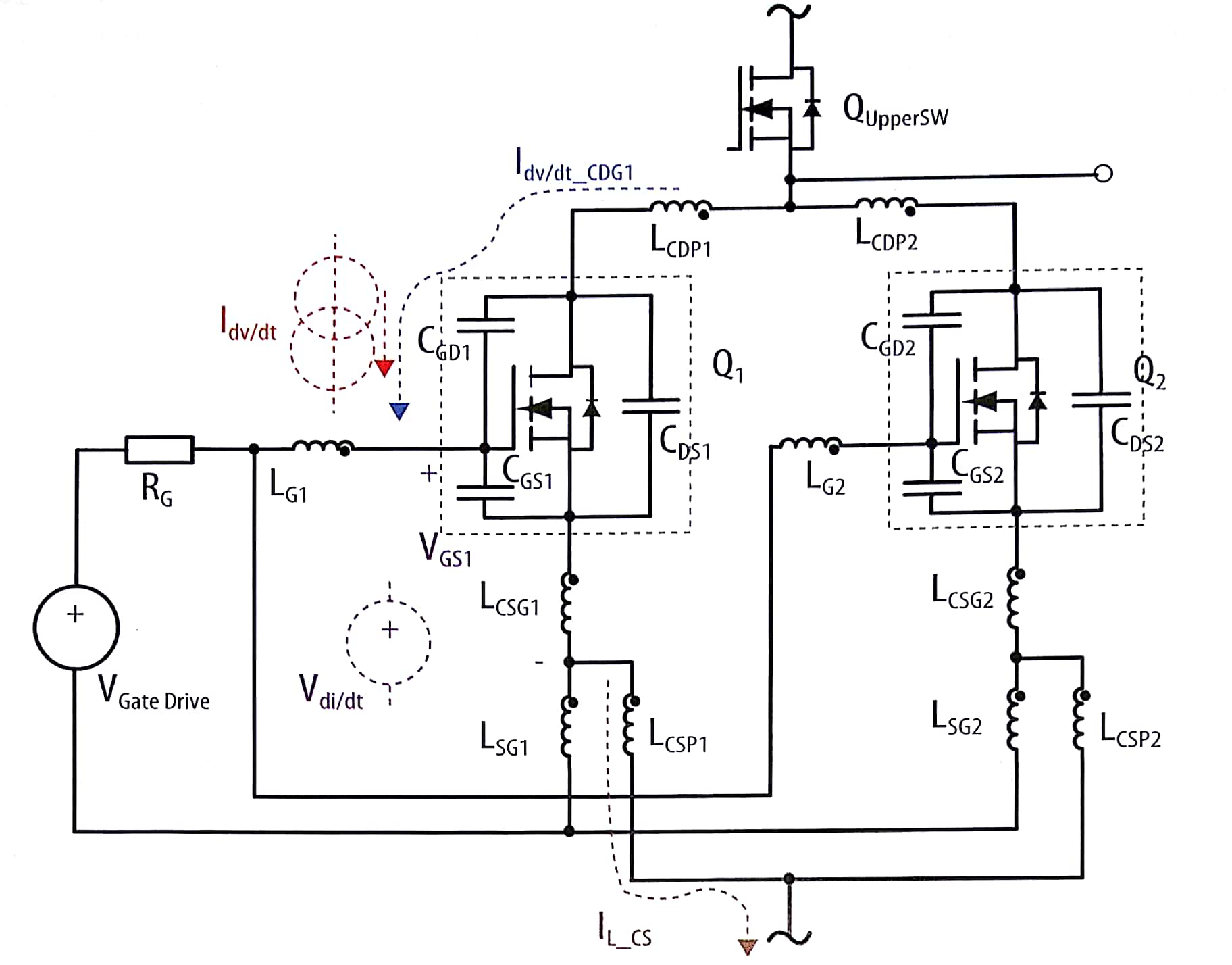

虽然包含栅极驱动器,栅机电路还是要求低阻抗,以确保开关中的器件栅极在dv/dt发生时保持关断状态。从图1和图2可以看出,栅极电路中有多个元素,包括:

·关断电阻(RGoff)

·栅极电路电感(LG)

·共源电感(LS)

·栅源电容(CGS)

·栅漏电容(CGD)

·栅极驱动器的关态电阻(RDR)(嵌入在Vgatedrive中

图1 并联两个场效应晶体管的一般电路,以展示器件与器件之间的寄生电感的位置

图2 使用简化的原理图来确定dv/dt(左图)和di/dt(右图)的抗扰度

在栅极电路的电感和电阻都是串联的,并在栅极至源极出现。开关的米勒电容CGD把不良电流引入栅极电路,而栅极电路中的电感器及电阻器的阻抗,将决定电压在栅极上的上升幅度。CGD相对漏极电压来说,是非线性的。评估板使用了以下电阻值:RDR=100mΩ和RGoff=1Ω。与栅极驱动器及栅极关断阻抗相比,栅极传输的走线电阻可以忽略不计,因为走线保持非常短小。

电路可以精简为跨CGS的电阻(RG+RDR)和电感(LG+LS)的串联。感应电流将在CGS和电阻-电感电路之间分配。dv/dt抗扰性电路的解决方案可以很复杂,因为一些方案可以包含振荡及指数部分。但可以肯定的是,我们应尽可能保持最小的电阻(RG+RDR)和电感(LG+LS),以确保最高dv/dt抗扰度。所有评估设计的电阻(RG+RDR)是维持相同的,因此所得结论是:抗扰度与电感(LG+LS)成反比。

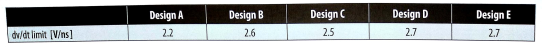

使用表1中的电感值及典型的阈值电压(VTH),我们得出每个评估设计在并联四个场效应晶体管时的di/dt极限值(见表3)。

表3 针对五个设计样例得出的dv/dt极限值