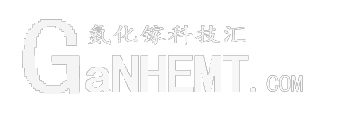

图1 一个简单的MOSFET结构

在Si MOSFET中,栅介质通过对Si衬底的热氧化得到,沟道由栅压在衬底所感生出来的反型电子层组成,器件的关断是通过源漏与衬底间形成的背靠背的p-n结实现,源漏的有源区及欧姆接触通过有源区的重掺杂及高温合金退火实现。而通过一系列工艺优化,Si MOS界面的界面态密度也被降到一个可接受的状态。而在GaN MOSFET中,这些关键点的实现又有所不同。

1. 离子注入工艺的GaN MOSFET

GaN MOSFET可通过与Si MOS类似的结构实现。由于GaN本征氧化物Ga2O3的禁带宽度较窄且与GaN衬底间的势垒高度低,导致以Ga2O3为介质层的器件的栅漏电流较大。与SiO2相比,Ga2O3不太合适作为栅氧。作为Ga2O3的替代,通过CVD、PVD等手段制作的SiO2、Al2O3等通常用来作为GaN MOSFET的栅氧化层。

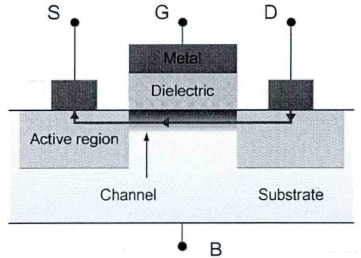

图2给出了基于离子注入工艺的GaN MOSFET的器件结构。这种传统结构的GaN MOSFET器件已经被一些研究者实现,这种结构的GaN MOSFET与传统的Si MOSFET类似,衬底采用P型或半绝缘GaN衬底,源漏采用离子注入或扩散等常规掺杂方式形成。然而,GaN中的离子注入或扩散工艺使得器件的制作工艺变得非常复杂。作为宽禁带半导体,GaN是一种非常稳定且坚硬的晶体。同时,GaN中常用的施主和受主杂质分别为Si和Mg,Si和Mg的离子半径及质量较大,这就决定了在离子注入过程中需要更高的能量且注入效率较低。更糟的是,GaN离子注入后需要高于1200℃的激活温度。所有这些过程都使得传统GaN MOSFET工艺更加困难、复杂且昂贵,对实验室的研究设备要求极高。

图2 基于离子注入结构的GaN MOSFET

2. AlGaN/GaN异质结结构的GaN MOSFET

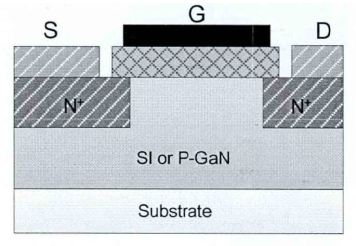

为了避免源漏离子注入及其高温退火所带来的复杂工艺,图3所示GaN MOSFET的结构成为了研究热点。这种工艺的出发点在于,MOSFET源漏的欧姆接触可以直接形成在GaN衬底上的AlGaN或者n-GaN外延上,栅可以形成在表面AlGaN或n-GaN被去除后的GaN衬底上。这就免去了离子注入制作源漏的复杂工艺,其难点在于栅区的干法刻蚀工艺。在这种结构中,一层薄的栅氧(通常栅氧厚度Tox≥100nm)被沉积在栅区沟槽上。也正是因为这种原因,栅区的沟槽刻蚀深度不能太深,因为深的沟槽将影响栅介质层在沟槽侧壁上的覆盖率。当栅介质覆盖率不好时,栅的漏电流将増大,严重情况下甚至会导致器件的失效。通常状况下,栅区的沟槽刻蚀深度应该小于氧化层的厚度(比如<100nm)。而且GaN上的AlGaN或者n-GaN外延层也应该小于沟槽的刻蚀深度,以保证器件的沟道形成在衬底的GaN上而不是在AlGaN或者n-GaN外延上。在实验中,氧化层的厚度通常被设定在60-100nm,栅区沟槽刻蚀的深度通常控制在40-50nm,用来形成源漏欧姆接触的AlGaN或n-GaN外延层的厚度通常为20-40nm。

图3给出了基于AlGaN/GaN异质结沟槽栅的GaN MOSFET结构。值得一提的是,结构中的AlGaN也可以用n-GaN层代替,但有一些潜在的缺点。如上段所述,作为外延的n-GaN层的厚度不可能太厚(约30nm),而且通过外延所得到的掺杂浓度不可能太高(通常ND≤1019cm-3),这样就导致了外延的薄膜电阻较大(20000Ω/□),而这些电阻成为器件的串联电阻,最终增加了器件的导通电阻,降低了器件的性能。

图3 基于AlGaN/GaN异质结的GaN MOSFET

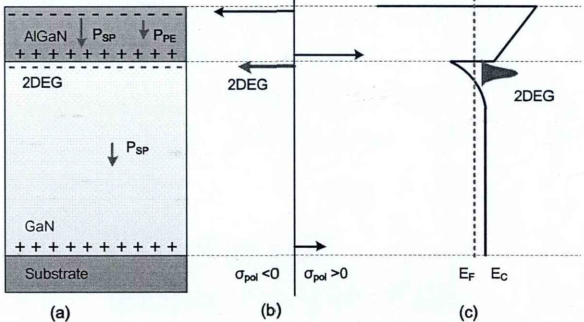

在AlGaN/GaN异质结结构上的源漏是一种很好的替代方案。AlGaN/GaN异质结所形成的特有的二维电子气(2DEG)具有高的电子密度(≥1013cm-2)。这种二维电子气的迁移率通常比GaN的体迁移率还高(≈1200cm2/Vs),其原因主要由以下几点:1)2DEG形成在掺杂浓度较低的GaN衬底一侧外,故二维电子气沟道衬底杂质散射较小;2)AlGaN与GaN晶格常数相近,晶格失配小,不会引起很多界面态;3)高浓度的2DEG会对库伦电场起到屏蔽作用,使得载流子受库伦散射变弱。高浓度与高迁移率两个特性相结合使得AlGaN/GaN异质结外延的方块电阻(400Ω/□)比相对应的n-GaN外延衬底要小很多。图3给出了基于AlGaN/GaN异质结带有沟槽栅的GaN MOSFET结构。实际上,这种AlGaN/GaN异质结结构所特有的二维电子气结构也是GaN区别于其它半导体的一个重要优势。与AlGaAs/GaAs异质结结构中主要来自于AlGaAs中的掺杂施主电离出的二维电子气沟道不同,AlGaN/GaN异质结中的二维电子气主要来自于AlGaN与GaN中的极化效应。极化效应产生的内建电势在GaN一侧形成了一个深且窄的电子势阱,GaN中的自由电子被吸引到这个势阱里形成AlGaN/GaN异质结所特有的二维电子气层。

图4展示了AlGaN/GaN结构中的各种极化情况及电荷分布,其中(a)极化情况(SP:自发极化:PE;压电极化),(b)极化电荷的分布情况,(c)被调制后的AlGaN/GaN异质结结构的能带结构。

图4 AlGaN/GaN异质结结构中的极化和电荷分布情况

AlGaN/GaN异质结结构存在一个问题,那就是源漏表面处的电子注入所引起的电流崩塌效应。电流崩塌效应会在源漏与栅间的扩展区产生虚栅效应,这种虚栅效应会使器件产生很强的回滞效应,使器件工作极不稳定。为了减轻这种效应,采用掺杂的AlGaN和GaN帽层,不仅可以有效降低电流崩塌效应,更可进一步降低外延层的方块电阻,从而进一步降低AlGaN/GaN异质结结构上GaN MOSFET器件的串联电阻。与AlGaN/GaN高电子迁移率晶体管(HEMT)不同,MOSFET的栅氧直接形成在沟槽刻蚀过的GaN上,所以AlGaN中的掺杂不会引起MOS栅漏电流的增加。

AlGaN/GaN异质结上的GaN MOSFET衬底的选择也是一个重要的问题。MOSFET的衬底需要能够在开启状态下提供载流子产生沟道,在关断状态下又可以有效阻止电流的流动。传统的MOSFET中,开启状态下的沟道由衬底反型出的反型电子形成,关断状态下,电流由衬底与源漏有源区所形成的背靠背的p-n结关断。然而,在AlGaN/GaN异质结上GaN MOSFET中采用p-GaN衬底,会出现以下缺点:1)p-GaN衬底不利于形成高密度的二维电子气层,进而会导致器件的串联电阻増大;2)GaN的P型掺杂剂(通常为Mg)激活率及电离率都非常低,这就导致了需要进行很大剂量的掺杂才能维持一个较低水平的自由载流子浓度(主要为空穴),而高的掺杂意味着更高的杂质散射和更差的晶体质量,从而使得器件的沟道迁移率降低。

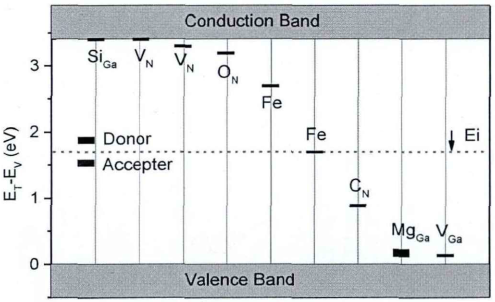

利用高电阻率衬底本身,也可以阻止电流流通,达到关断器件的目的。故而低掺杂且具有高电阻率的GaN可以被用来作为AlGaN/GaN异质结上GaN MOSFET的衬底。理想的高电阻GaN衬底应当是本征GaN,因为本征GaN具有10-10cm-3的本征载流子浓度,理论上具有非常高的电阻。然而,在实际情况下,非故意掺杂生长的GaN通常带有非常强的背景掺杂浓度(1015~1017cm-3),这些非故意掺杂来自于生长系统中的Si、O杂质,以及GaN本身的晶体缺陷如氮空位(VN)等。为了得到高电阻率的GaN衬底,除了采用各种方法降低背景掺杂外,通常还需要在GaN衬底中引入深受主能级,以补偿非故意的背景n型掺杂。经过近十年的研究,研究人员已经成功研制出了具有高电阻率的GaN衬底。区别于本征GaN,这种具有高电阻率的GaN通常被称为半绝缘GaN,其高电阻率是通过在GaN衬底中掺入Fe和C等杂质所实现的。Fe和C均会在GaN中产生比较深的受主能级,从而补偿背景中的自由电子。电阻率高达2x109Ω·cm的半绝缘GaN(SI-GaN)已经被报道。图5列出了GaN中一些重要的杂质能级在禁带中的相对位置。

图5 GaN中主要的杂质能级

除了衬底和外延层的选择,栅区的沟槽干法刻蚀工艺是实现AlGaN/GaN上GaN MOSFET的另一个难点。在栅区干法刻蚀过程中有几个基本要求,1)干法刻蚀的速度需要可控,因为栅区沟槽刻蚀的深度需要被控制在30-60nm左右;2)干法刻蚀过的表面需要非常平整且粗糙度较低,因为粗糙度大的界面会对沟道电子产生表面散射,降低器件的性能;3)干法刻蚀过程中的损伤和污染需要越小越好,因为损伤和污染可能在MOS界面引入界面态及杂质缺陷,从而因为杂质散射使得沟道的电子迁移率下降。