1. 界面电荷概述

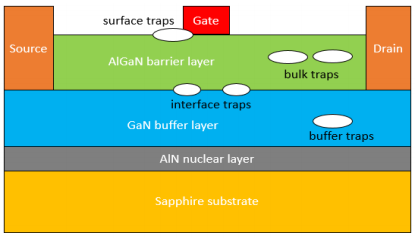

对GaN HEMT器件而言,影响器件性能的界面缺陷以及材料层体电荷有很多种,图1中给出了常规GaN基HEMT器件中界面与体电荷示意图。一般而言,我们将具有充放电效应的电荷称为陷阱,其中常见的包括体陷阱和界面态两种。而将不具有充放电效应的电荷称为固定电荷。对于Ⅲ族氮化物材料而言,材料中的电子陷阱主要来自于O元素掺杂,但是有关研究表明,由O掺杂引入的电子陷阱其陷阱能级一般都大于1eV,属于典型的深能级陷阱,因此充放电效应极其微弱。另外,对于常见的六方纤锌矿系的晶体结构而言,晶格结构的周期性排布规律在材料表面被中断,导致原本呈周期性分布的势场在晶体表面遭到破坏,从而在材料禁带中引入了额外的陷阱能级,形成了较多的表面悬挂键,这是氮化物材料中界面态的一个重要来源。在GaN HEMT器件中,稳定状态下的载流子陷阱(即电子陷阱)能级没有被电子填充,即处于电中性状态;而当给栅极加上正的偏置电压之后,沟道中的电子会被陷阱俘获,从而使得陷阱表现出负电性;当在直流偏置的基础上叠加一个交流信号时,对于发射时常数较大的陷阱态而言,由于陷阱中的电子跟不上交流信号的变化而不能及时从陷阱中释放,导致陷阱依旧处于被电子占据的状态,即陷阱带负电。

图1 常规GaN基HEMT器件中界面与体电荷示意图

从图1中可以看到,对于常规型GaN HEMT器件,根据各类电荷所处的纵向位置可以简单地将其分为器件GaN缓冲层陷阱、AlGaN/GaN异质结界面态、AlGaN势垒层陷阱以及器件表面陷阱等四部分。由于本章研究重点是AlGaN/GaN异质结的界面信息,因此在后续内容的分析中没有考虑器件表面态的影响。本文采用了环形肖特基二极管结构对栅下区域界面和固定电荷密度进行了定量分析,主要包括势垒层体陷阱和体固定电荷、异质结界面态和界面固定电荷、缓冲层体陷阱和体固定电荷以及表面电荷等几个部分。

2. 电导法简介

随着外加偏压的变化,半导体器件中所存在的体陷阱和界面态可以不断地释放或者俘获载流子,对于本文所研究的GaN HEMT器件而言,载流子指的就是沟道中的2DEG。在脉冲信号作用下或者器件的C-V测试中,陷阱中电子的发射速度如果慢于交流信号的变化,这将会引起所测的电子电流或者器件电容出现延迟,从这一延迟量中就可以计算出我们所关注的器件界面态密度。一般而言,GaN HEMT器件中的体陷阱主要来自于元素掺杂,并且多属于深能级陷阱,在没有受到额外的热激发或者光学照射等激励的条件下,氮化物材料中的深能级陷阱所对应的发射时常数都相当大,可以近似认为,在整个测试过程中氮化物材料中的体陷阱都是被电子填充的。另外,对于深能级陷阱相关信息的探测,需要运用特殊的测试技术,常规的电学方法(包括稳态、瞬态)难以胜任这一工作。因此,对GaN HEMT器件而言,本文采用变频电导法分析得到的的陷阱密度主要反映的是AlGaN/GaN异质结的界面态信息。

电导法是一种谱响应技术,是分析半导体器件界面态最常用并且最精确的方法之一,其测量精度可以达到109cm-2eV-1以下。这一测量技术的核心是基于MIS电容结构的等效并联电导Gp随偏置电压V和测试频率ω的变化曲线,其中并联电导Gp可以体现出界面态陷阱在俘获和释放沟道电子的过程中所引起的能量耗损,从中可以提取出界面态电荷密度。

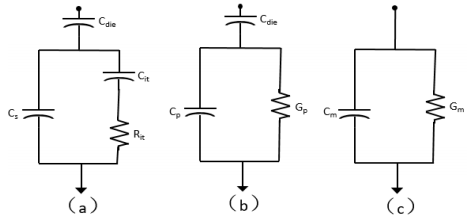

图2 电导法测试中等效电路图:(a)考虑界面态效应的MIS电容结构电路模型 (b)MIS电容结构简化电路模型(注:对我们所研究的器件绝缘层电容近似无穷大) (c)实际测试过程电容和电导并联模型

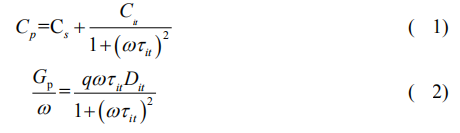

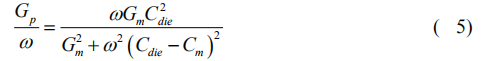

图2给出了电导法测试中所用到的等效电路图。图2(a)中,Cdie代表MIS结构绝缘层电容,Cs为半导体材料耗尽层电容,界面态的充放电过程用陷阱电容Cit表示,界面态的俘获和释放所伴随的能量损耗用陷阱电阻Rit表示,据此可以得到,界面态密度Dit=Cit/q,交流信号下陷阱发射时常数τit=Rit·Cit。为了计算方便,将图2(a)中的电路网表等效为2图(b)中的并联结构,其中Cp和Gp分别为并联电容和并联电导,这两个参数都与陷阱电容Cit和陷阱电阻Rit有关,都包含界面态相关的信息。由于界面态串联电路与并联电路是完全等效的,所以图2(a)和(b)所示电路两端的总阻抗和总导纳值也应该保持相等,由此可以将两个图中的元件参数联系起来,具体表达式为,

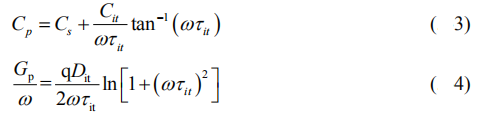

其中ω=2πf是角频率。需要声明的一点是,式(1)和(2)只有在单陷阱能级假设的前提条件下才能成立。但是一般情况下,界面态能级在禁带中都是呈连续性分布的,陷阱能级上的电子发射和俘获都是在半导体材料费米能级附近几个kT的能量范围内进行的,所对应的陷阱发射时常数离散化分布。基于连续陷阱能级所得到并联电容Cp和电导Gp经归一化处理可以表示为,

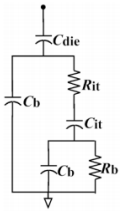

从式(3)和(4)中可以看到,与陷阱有关的并联电容Cp和并联电导Gp的表达式中都包括界面态密度和发射时常数,也就是说,电容法和电导法都可以用来分析和提取界面态相关的信息。但是,通过对比可以发现,电导表达式中不存在耗尽电容Cs的影响,因此采用电导法来提取界面态信息的过程将较为简单。另外,从上式可以看到,根据变频电导测量数据可以推导出Gp/ω~ω曲线,而这一曲线在ω≈2/τit处有最大值,且在曲线最大值点得出的陷阱密度Dit为2.5Gp/qω。但是,对MIS结构而言,在实际测试中并不能直接测得并联电导Gp的值,实际的测试模型如图2(c)所示,Cm和Gm是从电路两端直接测试得到的并联电容和电导,其中包含了绝缘层电容Cdie。再次利用电路等效原理,图2(b)和(c)两端得到的总阻抗和导纳应该相等,据此我们可以推导得到并联电导Gp与实测电导Gm和电容Cm之间的关系式,

电导法分析界面态的核心思路就是,根据测试所得的Cm和Gm,利用式(5)的关系得到Gp/ω~ω曲线,然后通过对曲线的最大值点的提取来得到AlGaN/GaN异质结的界面态密度和陷阱发射时常数等信息。

3. AlGaN/GaN异质结等效电路模型

电导法主要适用于器件电容-电压曲线的上升阶段,即对应于界面处半导体材料处在弱反型或者平带状态下的栅压区域,外加偏压的设置是否恰当将会直接影响测试结果的准确性。在本次实验中,我们主要通过提取变频C-V曲线的上升区域所对应的栅压范围来设置相应的偏压。另外,测试过程中所叠加的交流信号幅值应保持在50mV或者更低值,这样可以有效避免由谐波信号所引起的电导噪声,从而提高界面态相关参数的提取精度。基于此,本实验中采用的交流电压信号的幅值为30mV。

图3 栅压偏置在负压耗尽区时绝缘栅异质结构的等效电路简化图

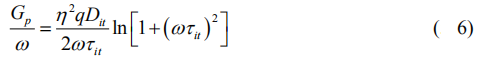

图3给出了偏置在负压耗尽区时GaN基绝缘栅异质结构等效电路简化图,可以看到,在简单MIS电容结构等效电路基础上,此模型中还加入了AlGaN势垒层的R-C阻抗网络,势垒层电阻和电容分别用Rb和Cb表示。另外,由于势垒层电阻一般都非常大,特别是在有AlN插入层的情况下更是如此,因此,与界面陷阱电阻Rit相比,可以近似认为势垒层电阻Rb→∞,即处于开路状态。引入参数η=Cb/(Cit+Cb),则并联电导可以用下面的表达式给出,

基于图3所示的等效电路结构,理想情况下,可以近似认为常规肖特基栅AlGaN/GaN异质结结构就是绝缘层厚度为0的绝缘栅异质结构,这也就意味着绝缘层电容Cdie趋于无穷大。