1. 常规HFET工作原理

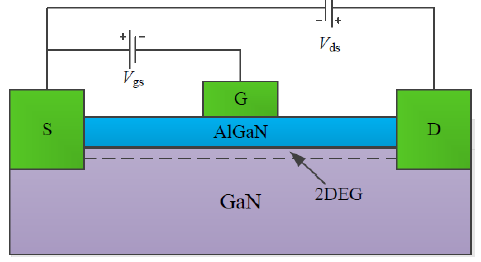

由于2-DEG的存在,常规HFET器件均为耗尽型(常开型)。器件工作时,通过外加偏置电压来调制2-DEG浓度和迁移率,图1所示为AlGaN/GaN HFET工作时的偏置电压情况,偏置电压不同,器件有不同的工作状态。从本质上讲HFET器件是一种场效应晶体管。栅源极偏压Vgs控制器件的开启和关断,漏源电压Vds形成横向电场,使2-DEG沿沟道输运形成源漏电流Ids,源端通常接地。

图1 AlGaN/GaN HFET工作时的偏压情形

当Vgs小于器件的阈值电压VTH时,器件处于截止状态,此时器件源漏电流Ids为关态漏电(主要由GaN缓冲层漏电和栅极肖特基反向漏电组成);当Vgs大于VTH时,又分为Vds较小时的线性工作区和Vds较大时的饱和工作区。

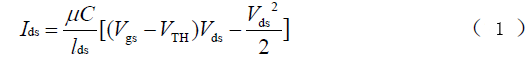

与Si基相同MOSFET相似,HFET工作在线性区时,输出电流Ids随漏源电压Vds线性增大:

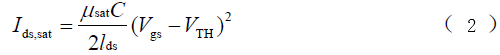

当Vds较大时,沟道内载流子达到速度饱和,源漏电流Ids也达到饱和,期间进入饱和区,饱和输出电流Ids,sat主要由Vgs控制,与Vds无关:

2. 增强型AlGaN/GaN HFET实现方法及工作原理

增强型器件具有误开启自保护功能(Fail-Safe),且仅需要单电源供电,因此在功率应用中通常选用增强型器件。由于强极化效应产生的高浓度2-DEG,常规AlGaN/GaN HFET器件为耗尽型器件,需要施加一个负的栅极电压才能使器件关断,毫无疑问这会额外增加系统功耗。所以增强型HFET器件一直都是业界的研究热点。本文将介绍目前已报道的几种增强型器件实现方法及其工作原理。

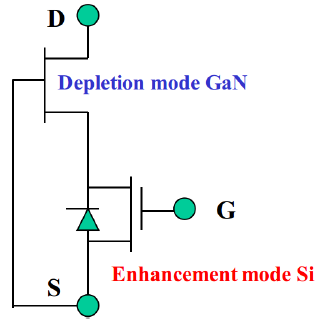

(1)Cascode级联技术

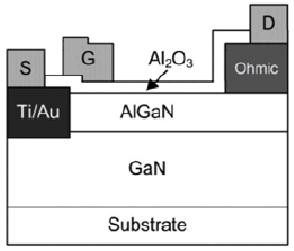

这是目前商用GaN功率器件主要采用的一种技术。将增强型Si基MOSFET与耗尽型AlGaN/GaN HEFT以如图2所示的方式级联成一个整体器件,整体器件的栅极为MOSFET栅极、源极为MOSFET源极、漏极为HFET漏极,通过控制增强型MOSFET实现高耐压增强型HFET。该HFET器件兼顾了增强型操作、电流密度大、击穿电压高等优点。该结构的缺点是开关功耗较大,同时额外引入的MOSFET增加了系统的体积和封装难度。

图2 基于Cascode结构的增强型AlGaN/GaN HFET结构图

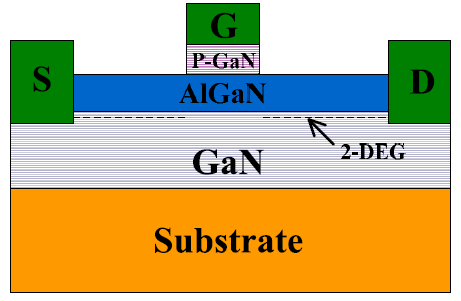

(2)P-gate技术

基于P-gate技术的增强型AlGaN/GaN HFET器件结构如图3所示。从图中可以看出,该技术主要通过P型GaN层与GaN缓冲层形成一个PN结,使沟道中的2-DEG耗尽,从而实现增强型AlGaN/GaN HFET。该技术的难点主要在于P型GaN难以获得,且难以实现在栅下的选择性生长。

图3 基于P-gate技术的增强型AlGaN/GaN HFET

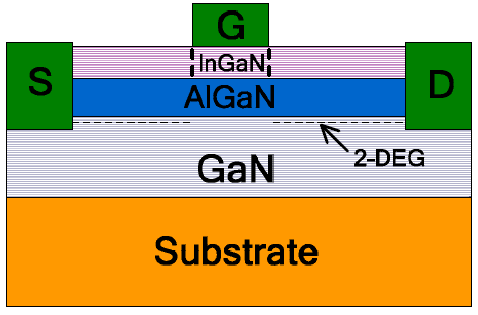

(3)极化抵消技术

在AlGaN势垒层上面增加一层极化方向与AlGaN极化方向相反的材料,通过栅极下方的极化抵消,来耗尽栅下沟道2-DEG,实现增强型HFET器件。结构图如图4所示。目前,增加的反向极化材料主要是InGaN。与P-gate技术相似,该技术难点也于栅极下方材料选择性生长。

图4 基于极化抵消技术的增强型AlGaN/GaN HFET器件结构

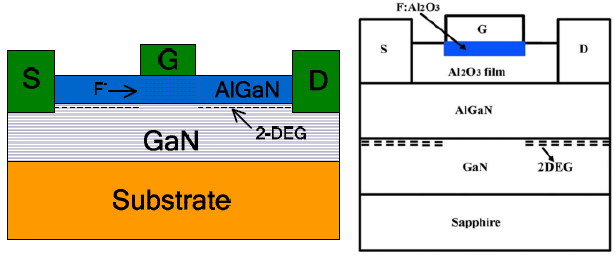

(4)负电离子注入技术

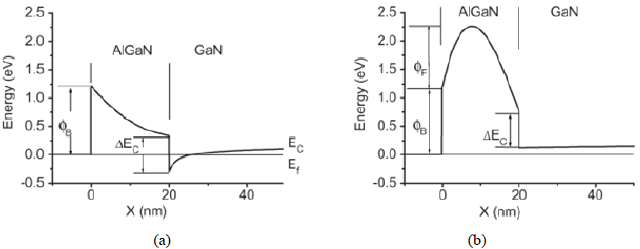

在栅极下方区域注入负电离子,负电离子的注入增大了半导体表面电势,从而耗尽栅下沟道的2-DEG,实现增强型器件。目前,较为成熟有AlGaN势垒层CF等离子注入和栅介质层CF等离子注入,分别获得了增强型HFET器件和增强型MIS-HFET器件,器件结构如图5所示。图6为负电离子引入前后,AlGaN/GaN能带图。目前,该术可能存在两个问题,其一为离子注入引发的晶体损伤,其二为长期可靠性有待进一步验证。

图5 采用氟离子注入技术的增强型器件(a)HFET;(b)MIS-HFET

图6 栅极区域能带图(a)未注入氟离子;(b)注入氟离子后

(5)GaN隧穿结场效应晶体管(TJFET)

由于AlGaN/GaN异质结界面处具有很高的2-DEG浓度,Yuan Li等人通过将tunnel FET的结构引入到GaN器件中,实现了增强型HFET器件。图7为GaN TJFET的示意图,与常规HFET不同之处在于,器件源极为凹槽结构,源极为肖特基接触,源极金属处于凹槽之中与2-DEG沟道直接接触。TJFET的栅极覆盖着源极金属与2DEG沟道的交界部分。从工作原理上来看,TJFET与传统的硅基TFET相同,只是隧穿发生在肖特基结而非PN结。GaN TJFET因工艺复杂,目前难以实现大规模量产。

图7 采用隧穿结构的增强型AlGaN/GaN HFET

(6)凹槽栅技术(Recessed-Gate)

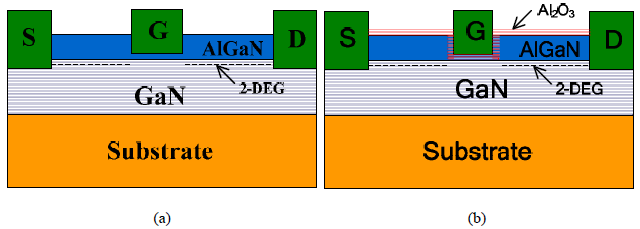

凹槽栅技术主要使用干法刻蚀工艺减薄栅极下方AlGaN势垒层厚度以降低异质结极化作用,从而耗尽沟道中的2-DEG,实现增强型器件。当前主要有两种凹槽栅器件,其一为仅进行栅下势垒层减薄的HFET结构,如图8(a);其二为在栅下势垒层减薄后淀积栅介质的MIS栅HFET结构,如图8(b)。

图8 凹槽栅AlGaN/GaN增强型器件(a)HFET;(b)MIS-HFET

早期,凹槽栅技术主要用于制备凹槽HFET器件,2005年W.B.Lanford等人使用BCl3/Cl2等离子体进行干法刻蚀凹槽栅,在栅下势垒层厚度剩余8nm时,实现了+0.47V阈值电压为的增强型HFET;为修复干法刻蚀后的晶格损伤,该实验在刻蚀后进行了高温退火工艺。使用BCl3/Cl2等离子体进行干法刻蚀,这种方法形成凹槽的效率高,但其缺陷是速率不易控制、刻蚀后表面粗糙度高且刻蚀造成的晶格损伤会大大降低增强型沟道中的2-DEG迁移率从而大大降低增强型器件的性能。2010年,S.D.Burnham等人使用O2-BCl3等离子体代替BCl3/Cl2等离子体进行干法刻蚀,这种工艺可以改善刻蚀后材料表面形貌并显著降低干法刻蚀造成的表面晶格损伤,获得了性能较佳的增强型HFET器件,但因刻蚀后势垒层较薄,在Vgs=2V时栅泄漏电流已达0.1mA/mm,同时这种增强型器件的阈值电压较低(约为0.5V),在Vgs=0V时关态泄露电流较大。因种种弊端这种器件无法实现商业化应用。

2008年T.Oka等人首次提出了MIS栅增强型高压功率HFET。这种MIS栅HFET通过在栅极区域采用积累层电子沟道,而在接入区采用异质结2-DEG沟道,结合了MIS器件与HFET器件的优点,同时通过加入栅介质,既大幅降低了栅极泄漏电流又大幅增加了栅电压摆幅和栅可靠性,成为更有前景的一种增强型器件结构。